tugas pendahuluan 2.5

TUGAS PENDAHULUAN 2

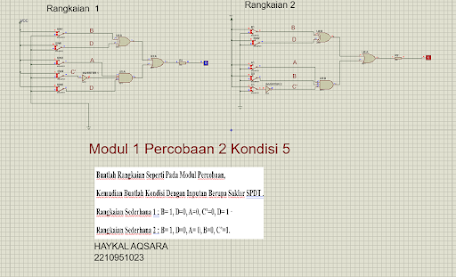

Rangkaian Sederhana 1 : B= 1, D=0, A=0, C’=0, D= 1

Rangkaian Sederhana 2 : B= 1, D=0, A= 0, B=0, C’=1

4. Prinsip Kerja [Kembali]

Rangkaian Sederhana 1: Pada rangkaian ini, kondisi input logika adalah B = 1, D = 0, A = 0, C' = 0, dan D = 1, dengan saklar bagian D yang terhubung dengan Vcc sehingga berlogika 1. Pada gerbang XOR, inputnya berasal dari B dan D, dengan nilai logika masing-masing 1 dan 0. Gerbang XOR akan memberikan output 1 jika jumlah input bernilai ganjil, karena 1 + 0 adalah ganjil, maka output XOR menjadi 1. Selanjutnya, pada gerbang AND dengan 3 input, yaitu A = 0, C = 0 (diubah menjadi C' = 1 oleh inverter), dan D = 1, aturan gerbang AND menyatakan bahwa jika ada satu saja input bernilai 0, maka output akan menjadi 0. Output ini kemudian diteruskan ke gerbang OR, yang memiliki sifat bahwa jika ada satu input bernilai 1, maka output akan menjadi 1. Karena input dari gerbang XOR adalah 1 dan dari gerbang AND adalah 0, maka output dari gerbang OR adalah 1, yang ditunjukkan oleh logic probe berlogika 1.

Rangkaian Sederhana 2: Pada rangkaian kedua, input logika yang diberikan berbeda yaitu B = 1, D = 0, A = 0, B = 0, dan C' = 1. Pada gerbang XOR, input yang masuk adalah B dan D dengan nilai logika masing-masing 1 dan 0. Karena penjumlahan logika tersebut menghasilkan nilai ganjil, output dari gerbang XOR adalah 1. Selanjutnya, pada gerbang AND, input A dan B masing-masing bernilai 0, sedangkan C bernilai 1. Namun, terdapat gerbang NOT pada input C yang mengubah nilainya menjadi C' = 0. Karena ada input yang bernilai 0, maka output dari gerbang AND adalah 0. Output ini kemudian diteruskan ke gerbang OR, yang memiliki input dari XOR dan AND dengan nilai masing-masing 1 dan 0. Sesuai dengan sifat gerbang OR, outputnya menjadi 1, yang juga ditunjukkan oleh logic probe berlogika 1.

5. Link Download [Kembali]

Komentar

Posting Komentar